# IQ-GraphBlit - High-Performance 2D Graphic Accelerator

### Description

IQ-GraphBlit is a light-weight, performance 2D graphic accelerator IP core. It performs fast bitmap copy operations with support for ROP2 raster logical operations, solid fills, pattern generation and color depth conversion.

The blitting engine also supports Porter-Duff alpha blending operations allowing compositing of semitransparent images to obtain advanced rendering effects. Alpha masking support allows for operations such as font texturing and image clipping.

The core is accompanied with comprehensive driver and API suite supporting the entire core functionality, and allowing also accelerated rendering of graphic primitives such as lines and rectangles.

It integrates easily with Lattice's Diamond and Altera's SOPC builder tools.

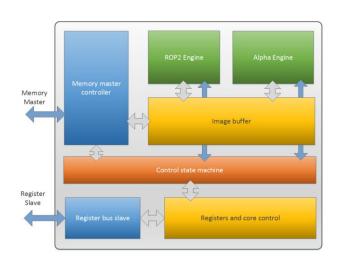

### **Block Diagram**

14.5.2015

Rev. 1.3

### **Implementation**

#### **Altera Cyclone III (EP3C16)**

Basic version (No alpha blending)

| LEs  | BRAMs (M9K) | Multip. | F <sub>max</sub> | IO Pins |

|------|-------------|---------|------------------|---------|

| 2838 | 2           | 0       | 143 MHz *        | 195 **  |

#### Full version (Alpha blending included)

| LEs  | BRAMs (M9K) | Multip. | $F_{max}$ | IO Pins |

|------|-------------|---------|-----------|---------|

| 3233 | 2           | 4       | 137 MHz * | 195**   |

#### Lattice (ECP3-35EA)

Basic version (No alpha blending)

|       |      | •    |         |                  |         |

|-------|------|------|---------|------------------|---------|

| LUT4s | Regs | EBRs | Multip. | F <sub>max</sub> | IO Pins |

| 2630  | 1381 | 2    | 0       | 199 MHz *        | 195 **  |

#### **Full** version (Alpha blending included)

| LUT4s | Regs | EBRs | Multip. | F <sub>max</sub> | IO Pins |

|-------|------|------|---------|------------------|---------|

| 2981  | 1526 | 2    | 4       | 183 MHz *        | 195**   |

- Maximum frequency of the system bus interface, for AMBA AHB

- Assuming all core ports routed off-chip

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders shall be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved. Technical data is subject to change at any time.

#### Copyright © 2015 Mikroprojekt Ltd. All Rights Reserved.

### Feature highlights

#### Basic rendering operations

The core allows basic rendering applications such as image copy, solid color fill and text rendering.

ROP2 operations allow for rendering of sprites over image backgrounds, such as Windows icons.

The configurable memory interface, supporting two independent source pointers and a destination pointer with configurable stripe and color depth, allows efficient memory use and organization.

#### Alpha blending

Alpha blending allows the rendering of high quality antialiased graphical elements and images by allowing edge antialiasing through semitransparent pixels.

Advanced image compositing and combining is supported through Porter-Duff alpha blending operations, allowing for blending, clipping, overlaying, exclusion and other graphic effects.

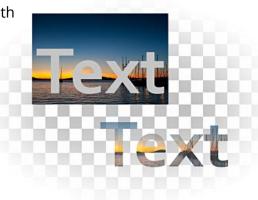

#### Font texturing

Alpha blending operations in conjunction with alpha masking enables high quality type and font rendering with antialiased edges employing an alpha mask to render fonts.

An alpha mask can be generated by a standard, open source type rendering library such as FreeType, which allows rendering of TrueType and OpenType fonts

### **Applications**

- Vending machines

- Video monitors

- Automotive infotainment

- Medical instrumentation

- Human machine interface (HMI) systems

- Mobile devices

bitmaps

Alpha masking of RGB

Rev. 1.3

14.5.2015

- Versatile pattern fill operations

- Solid color fill

- Color-key transparency

- Color depth conversion from any to any RGB format

#### **Deliverables**

- Encrypted RTL source code supporting SOPC builder (Altera) / Precompiled IP core in desired configuration (Lattice)

- Testbench

- Datasheet

- User manual

- Implementation guide

#### Verification

The core has been rigorously tested in functional simulation and actual hardware. The core is accompanied with automated testbench with automated testbench with a system bus master simulation model and a system bus slave simulation model.

#### **Features**

#### **Supported graphical operations**

- Raster image move and copy

- ROP2 binary raster operations

- o 16 ROP2 operations

- Alpha blending operations

- 4 basic Porter-Duff alpha blending operations

## Additional capabilities

- Configurable memory access

- 2 dedicated source pointers and 1 destination pointer

- Fully configurable copy source and destination addresses

- Source and destination bitmap resolutions up to 131071x131071

- Bitmap stripe size fully configurable

- Extensive pixel format support:

- 8-bit RGB (3:3:2)

- 16-bit RGB (5:6:5)

- o 24-bit RGB/BGR

- 32-bit ARGB/ABGR

- o 8-bit alpha bitmasks

- Available interrupt output

- Fully compatible with AVALON system bus and SOPC Builder

- Integrated DMA memory master supporting low-overhead burst transfers

- Master bus interfaces

- AMBA AHB

- AMBA AXI4

- Avalon

- Peregrine\*

<sup>\*</sup> Peregrine bus is Mikroprojekt's proprietary bus architecture, optimized for FPGA architecture

### Contact info

### Mikroprojekt Ltd.

Aleja Blaža Jurišića 9 HR-10040 Zagreb Croatia

tel/fax +385 1 2455 659

mail: contact@mikroprojekt.hr

web: http://www.mikroprojekt.hr