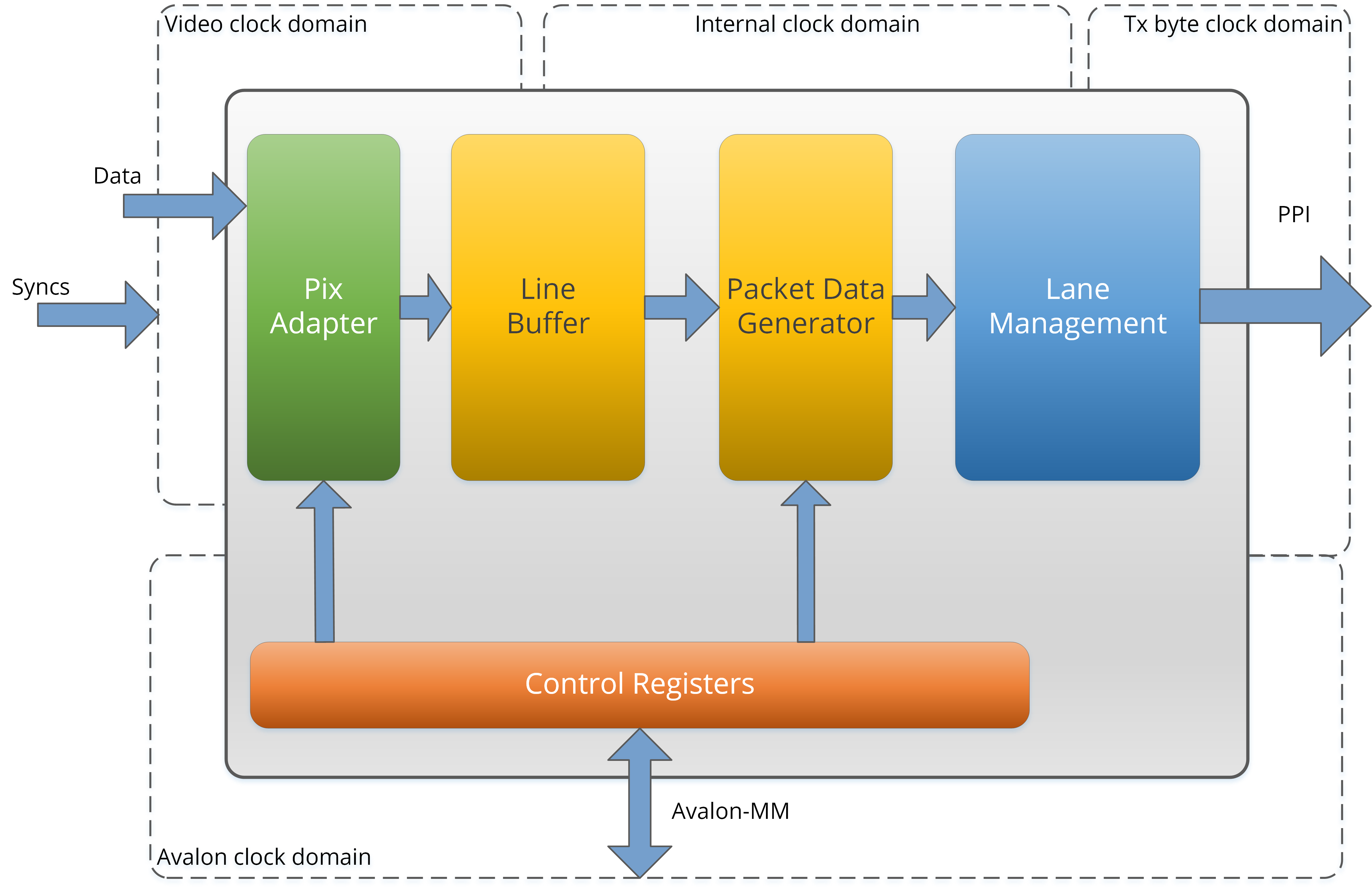

IQ-CSI-Tx is a MIPI CSI-2 protocol engine/ transmitter IP core designed to work with PPI-compatible MIPI D-PHY serial interfaces for driving MIPI based image sensor processors.

MIPI CSI-2 Transmitter IP core (IQ-CSI-Tx) together with DPHY-Tx IP core provides high speed serial interface to MIPI CSI-2 compliant application processors or image sensor processors.

MIPI CSI-2 Transmitter converts a standard parallel video interface into CSI packets transferred to the physical layer (MIPI D-PHY) through the PHY Protocol Interface (PPI) recommended by the MIPI Alliance.

Key feature Set

- Clocked video interface at input

- PHY-Protocol Interface (PPI) towards D-PHY

- Data rate from 80 to 900 Mbps per lane

- Supports all primary video data formats (RAW, YUV, RGB)

Commercial applications

- Camera interfaces

- Automotive infotainment

- Drones/UAVs

- Industrial

- Medical

Feature List

- Programmable number of serial data lanes (1-4)

- Data rate from 80 to 900 Mbps per lane

- PHY-Protocol Interface (PPI) towards D-PHY

- Clocked video interface at input

- HS (High Speed) mode transmission support

- LP (Low power) insertion between the packets

- Supports all primary video data formats (RAW, YUV, RGB)

- ECC generation for packet header

- CRC generation for packet payload

- Avalon-MM interface for register access

- Compliant to MIPI Alliance Specification for Camera Serial Interface v1.3.1

![]()

Please contact us via email This email address is being protected from spambots. You need JavaScript enabled to view it. about item availability and ordering details.

Thank you!